**Pervasive and Emerging Architecture Research Lab (PEARL)**

### Enabling Efficient SIMD Acceleration for Virtual Radio Access Network

DALLAS

Jianda Wang\*, Yang Hu

ICPP 21'

Pervasive and Emerging Architecture Research Lab, UT Dallas

**Pervasive and Emerging Architecture Research Lab (PEARL)**

#### 1. Motivation and Background

#### 3. vRAN Inefficiency and Optimization

#### 2. Architectural Implications of vRAN

DALLAS

#### 4. Evaluations

#### Pervasive and Emerging Architecture Research Lab (PEARL)

# **UT** DALLAS

#### 1. Motivation and Backgrounds

#### **Home Automation**

#### **Autonomous Driving**

#### New Era Network

#### Smart City

#### Healthcare

Virtual Reality

Pervasive and Emerging Architecture Research Lab (PEARL)

#### 1. Motivation and Backgrounds

**New Era Network**

UT DALLAS

Pervasive and Emerging Architecture Research Lab (PEARL)

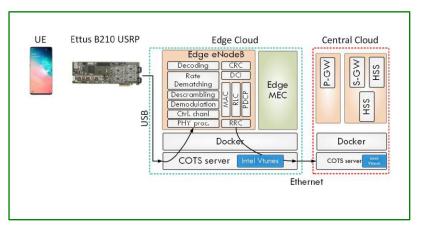

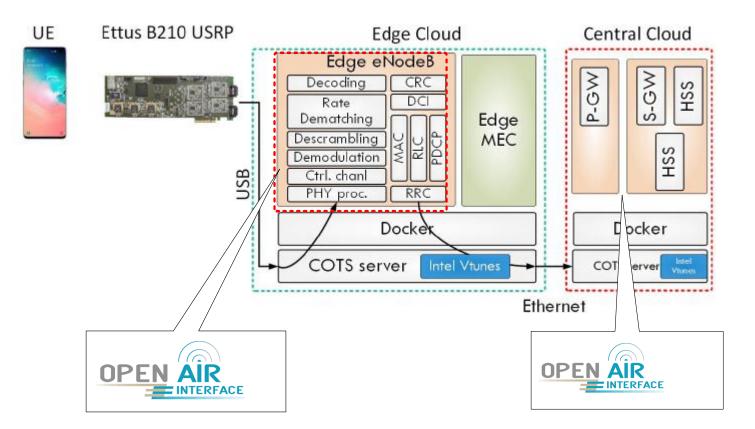

#### 1. Background – Typical vRAN Architecture

OpenAirInterface 2018\_w25 (eNodeB)

**OpenAirInterface Version Develop**

UT DALLAS

**Pervasive and Emerging Architecture Research Lab (PEARL)**

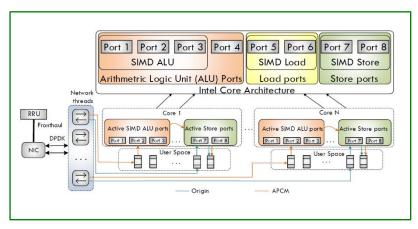

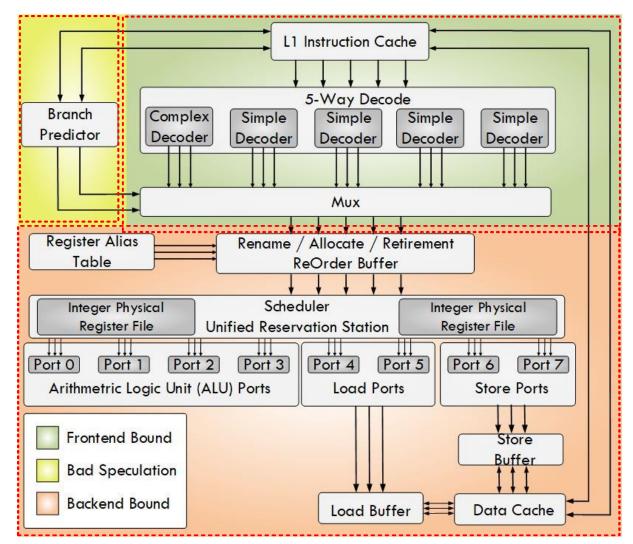

#### 1. Background – Typical Intel Core Architecture

• Frontend Bound

UT DALLAS

- Bad Speculation

- Backend Bound

Pervasive and Emerging Architecture Research Lab (PEARL)

#### 2. Architecture Implications of the RAN system

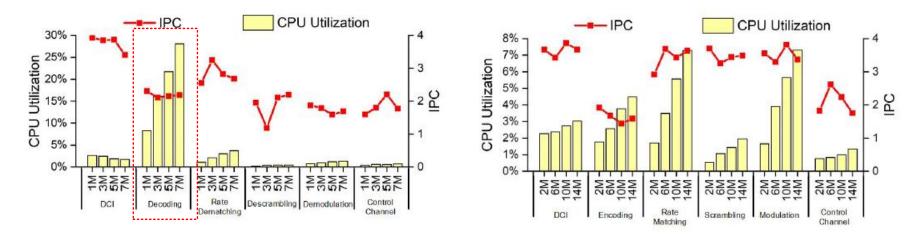

#### **IPC and CPU Utilization**

- We can observe that for both uplink and downlink cases, the IPCs for Downlink Control Information (DCI), Rate Matching, and Scrambling are near to the ideal value of 4 for modern Intel processor. All these modules are not CPU consuming.

- However, the IPC for the most CPU consuming module Turbo Decoding is only around 2.1, which suggests potential headroom for optimization.

Pervasive and Emerging Architecture Research Lab (PEARL)

#### 2. Architecture Implications of the RAN system

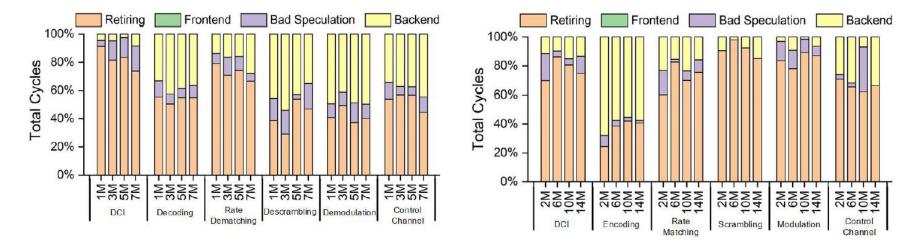

#### Micro-architecture value for the RAN system

DALLAS

- As demonstrated in the micro-architectural profile, the results reveal that across all the modules, the frontend bound and bad speculation overheads are negligible.

- The main stall of vRAN applications are concentrated on the backend bound, which means the optimization for backend bound is necessary for vRAN applications.

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

#### 2. Architecture Implications of the RAN system

#### Wimpy and Beefy node Setup

|          | Wimpy Node | Beefy Node |

|----------|------------|------------|

| L1 cache | 384KB      | 1152KB     |

| L2 cache | 1536KB     | 18432KB    |

| L3 cache | 12288KB    | 25344KB    |

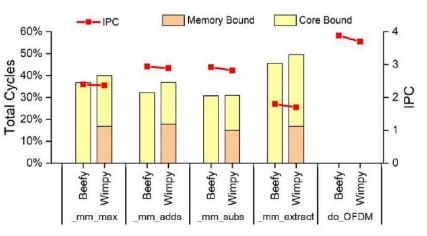

## IPC, memory and core bound under wimpy and beefy node

ALLAS

The figure shows the memory bound and core bound on the wimpy server and the beefy server. Our finding is that although the memory bound is significantly mitigated by the larger cache resources, the core bound overhead becomes worse on the beefy server. The counteracts of the lower memory bound and the higher core bound on beefy server platform makes the overall backend bound stay almost the same to the wimpy server platform.

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

#### 2. Architecture Implications of the RAN system

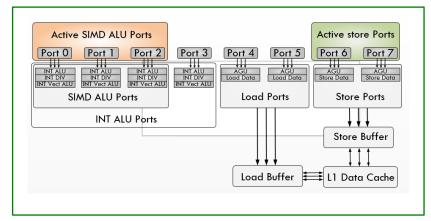

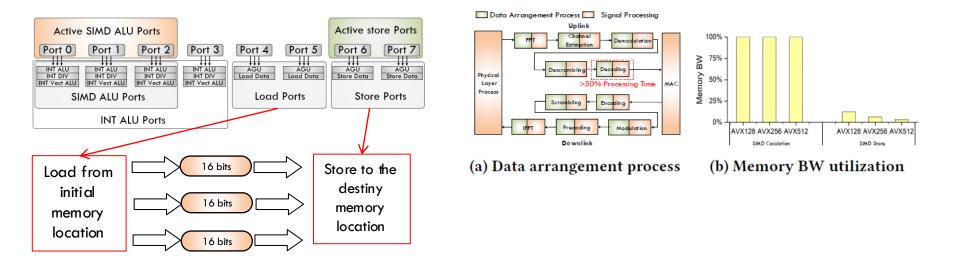

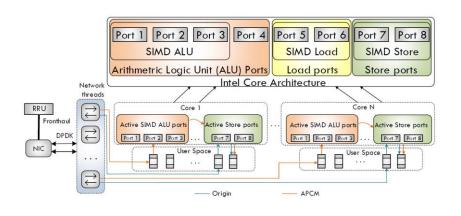

#### Active SIMD ALU Ports Active store Ports Port 1 Port 3 Port 6 Port 0 Port 2 Port 4 Port 5 Port 7 AGU INT ALU INT ALL INT ALL INT DIV INT DIV INT DIV Physical Load Data INT Vect ALU INT Vect ALU Layer INT Vect AL Process SIMD ALU Ports Load Ports Store Ports INT ALU Ports

#### Intel processor architecture

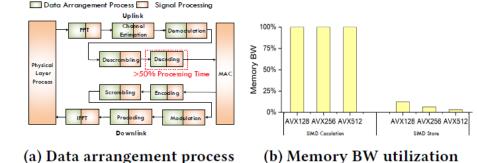

## Data arrangement process inefficiency for the RAN system

DALLAS

Our profiling reveals that the data arrangement process suffers severe low memory bandwidth utilization between the ports' registers and L1 cache since it only utilizes the load and store ports in the processor

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

#### 2. Architecture Implications of the RAN system

#### Intel processor architecture

### Data arrangement process inefficiency for the RAN system

DALLAS

• The bandwidth utilization for the original process is 16 bits/cycle

#### Pervasive and Emerging Architecture Research Lab (PEARL)

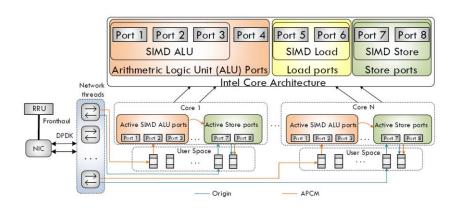

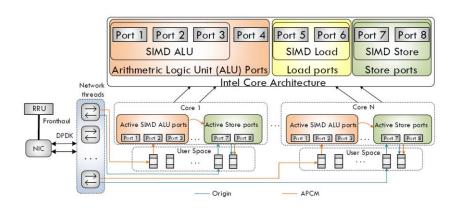

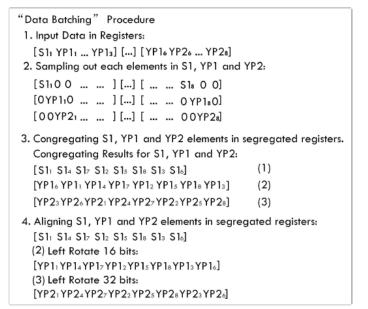

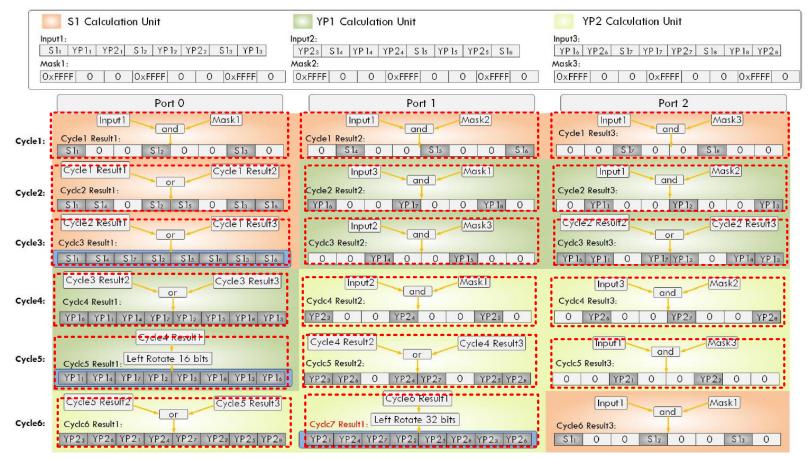

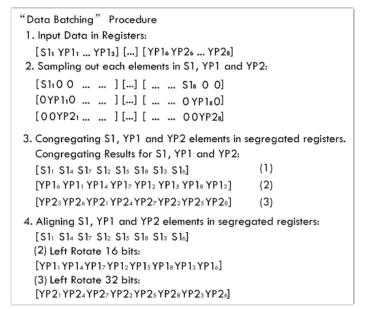

#### 3. Optimization of the current RAN system

#### Data arrangement process under APCM

DALLAS

We propose "Arithmetic Ports Consciousness Mechanism" (APCM) to leverage these idle ALU ports concurrently with the load and store ports to solve the data arrangement inefficiency problem.

#### Pervasive and Emerging Architecture Research Lab (PEARL)

#### 3. Optimization of the current RAN system

#### Data arrangement process under APCM

DALLAS

As shown in the figure, after the data is transferred directly into the user space by DPDK, APCM utilizes the ALU ports to batch the data before storing them back to the cache. This will alleviate the backend bound and meanwhile promote the bandwidth utilization between the registers and the cache.

#### Pervasive and Emerging Architecture Research Lab (PEARL)

# UT DALLAS

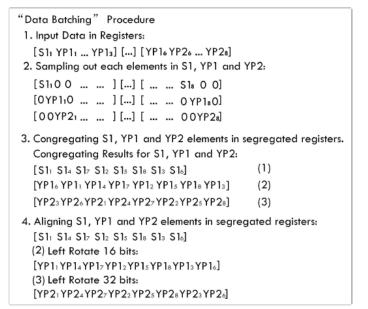

#### 3. Optimization of the current RAN system

#### Data arrangement process under APCM

#### Pervasive and Emerging Architecture Research Lab (PEARL)

#### 3. Optimization of the current RAN system

#### Data arrangement process under APCM

DALLAS

Based on the procedure of the APCM mechanism, we can calculate that the bandwidth per cycle under APCM will be around 67 bits/cycle, 134 bits/cycle and 270 bits/cycle for the SSE128, AVX256 and AVX512.

### DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING Pervasive and Emerging Architecture Research Lab (PEARL)

#### 4. Evaluations

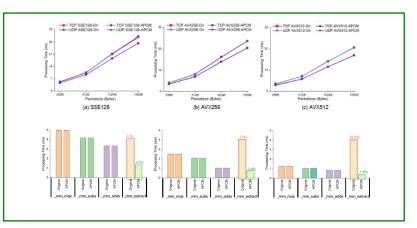

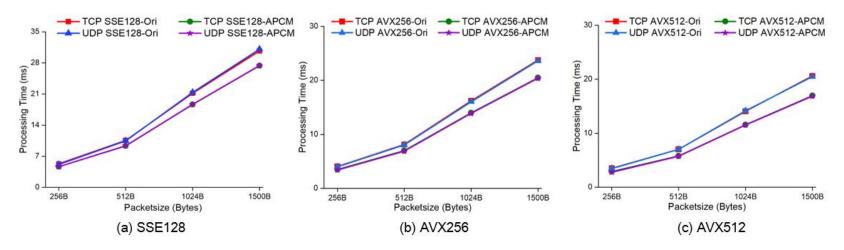

#### Processing time for UDP and TCP under different packetsize with original and APCM

• The figure demonstrates the APCM decrease the processing time for both UDP and TCP packet from 12% (SSE128) to 20% (AVX512).

#### Pervasive and Emerging Architecture Research Lab (PEARL)

#### 4. Evaluations

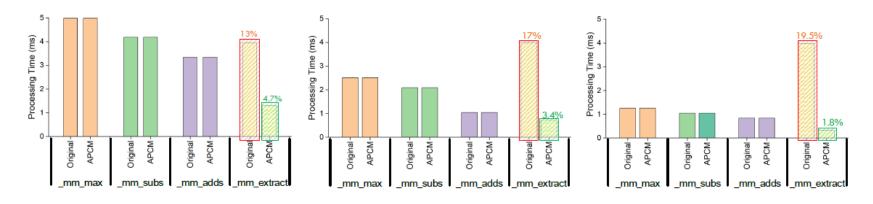

#### SIMD Module Processing Time under SSE128, AVX256 and AVX512

DALLAS

• For the registers with the width 128 bits, 256 bits and 512 bits, the data arrangement process time proportion decrease from 13%, 17%, and 19.5% to 4.7%, 3.4%, and 1.8%.

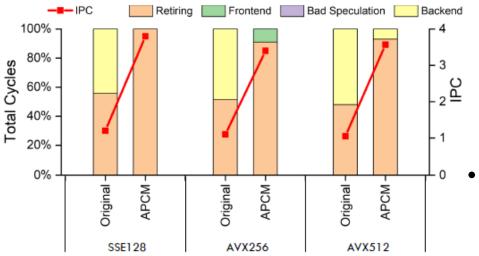

#### 4. Evaluations

#### Microarchitectural Value under Original Mechanism and APCM

As shown in the figure, we can observe that for registers with the width 128 bits, 256 bits and 512 bits, the retiring percentage increases from 55%, 52% and 48% to 97%, 96% and 95%. The main backend bound stall decreases from 44%, 48% and 52% to 3%, 4% and 5%.

DALLAS

The IPC soars from 1.2, 1.1, and 1.05 to 3.6, 3.5, and 3.3.

#### 5. Questions?