# ArchViMP - a Framework for Automatic Extraction of Concurrency-related Software Architectural Properties

Monireh Pourjafarian

mpourjaf@rhrk.uni-kl.de

Technical University of Kaiserslautern

Kaiserslautern, Germany

#### Jasmin Jahić

jj542@cam.ac.uk

University of Cambridge

Cambridge, UK

## INTRODUCTION AND MOTIVATION

Concurrent software is complex.

There are many dependencies between threads

Why complexity is important?

Implicit dependencies and high-coupling

Concurrency-related architectural properties:

- Data dependency

- Functionality

Problem: Comprehension of many dependencies between threads is hard.

Solution: Make understanding easier through a visual representation of analysis thread interdependencies based on the architecture principles.

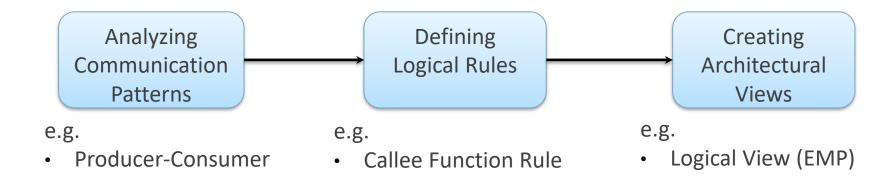

## Methodology and Contribution

We made understanding of a concurrent software easier by providing:

- A set of abstraction rules that helps with reducing the number of elements and relations in screen

- A set of architectural views that helps the user to observe the software analysis from a different viewpoint

## Methodology and Contribution

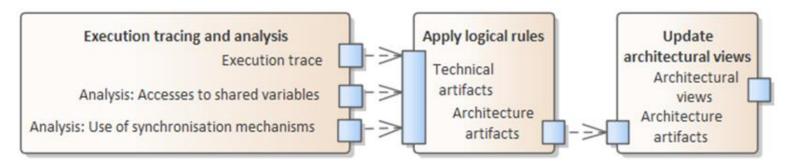

BOSMI: A Framework for Non-intrusive Monitoring and Testing of Embedded Multithreaded Software on the Logical Level

Overview of ArchViMP Architecture

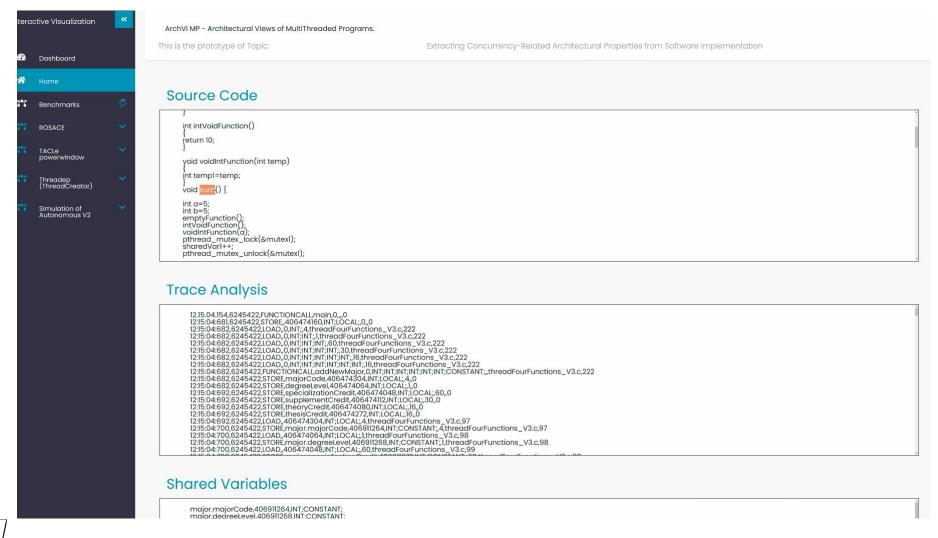

Architectural Views for Multithreaded Programs (ArchviMP) is implemented as a web-based prototype <a href="https://mpourjafarian.github.io/ArchViMP.github.io/">https://mpourjafarian.github.io/ArchViMP.github.io/</a>

## Logical Rules

- Technical data and components vs Logical data and components

- 1. The Data Structure Rule (DSR) groups shared variables declared within the same data structure (e.g., union, struct).

- 2. The Entry Point Function Rule (EPFR) abstracts the functional behaviour of threads by grouping those with the same functionality.

- 3. The Thread Operation Rule (TOR) creates groups of shared variables based on the common operation types (Input, Output, and Process).

- 4. The Thread Data Access Rule (TASR) represents a combination of the EPFR and TOR rules to complete the behavioural representation of thread communication over shared variables.

- 5. The Callee Function Rule (CFR) abstracts logical data as a group of shared variables that have been accessed by a single or group of logical components within a callee function, by identifying function calls of the logical component and shared variable they accessed inside each callee function.

- 6. The Logical Decision Rule (LDR) shared variables that are only accessed by an individual or group of logical components under a logical decision (not being a part of a logical decision but accessed after the decision is evaluated to true) are grouped as a logical data.

- 7. The Time Span Rule (TSR) if threads access shared variables, they are then grouped according to the user-defined time intervals.

# Architectural Views for Concurrency-related Software Properties

- 1. Context

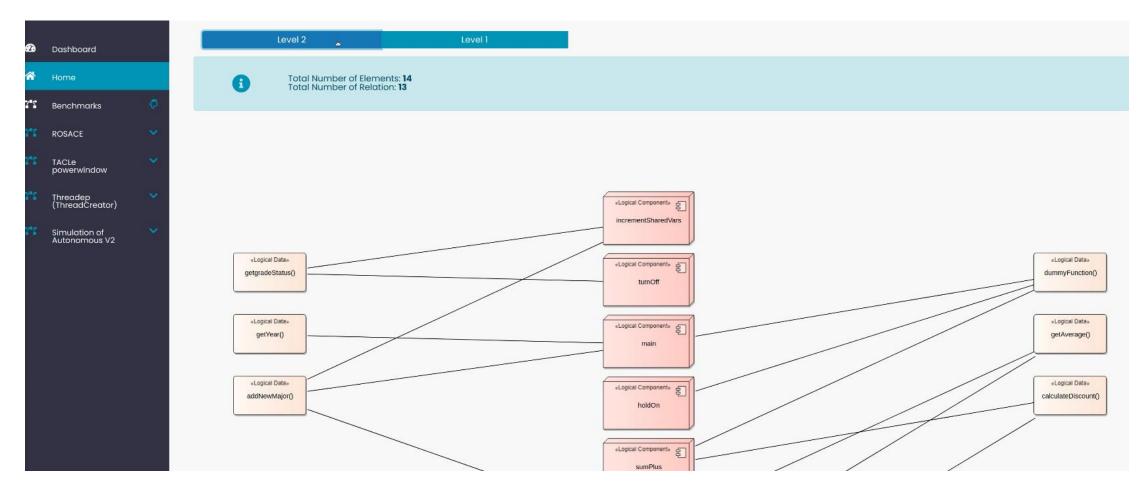

- 2. Functional Concurrency View

- a. Functional Flow Sub-view

- b. Execution Control Flow Sub-view

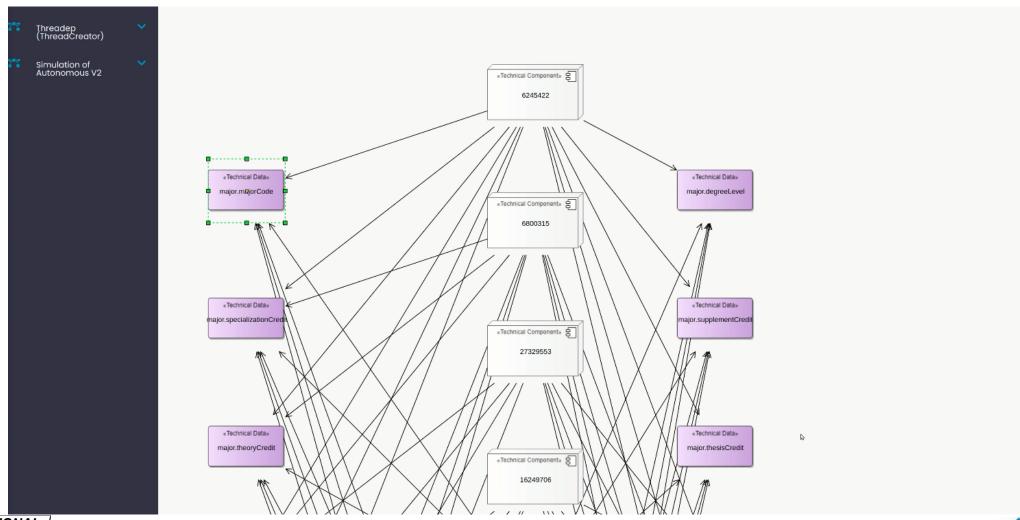

- 3. Technical Concurrency View

- a. Logical Component Sub-view

- b. Data Structure Sub-view

- c. Data Type Sub-view

- 4. Timeline Concurrency View

#### **Levels of Abstraction**

starting from level 3 as the highest level to level 0 as the lowest level of abstraction.

**Level 3**: Defines the architectural view that illustrates direct access dependencies between group of logical components over group of shared variables (logical data).

**Level 2**: Describes the architectural perspectives that show how logical components interact with technical or logical data groups.

**Level 1**: Defines the architectural views that display the members of logical groups, either logical components or logical data.

**Level 0**: This level is the raw visualization of trace execution data which depicts only the technical elements of the concurrent software and raw connection between them (i.e., pure technical implementation details).

## DEMO

ArchViMP framework

# Example

# Example

# Example

# EVALUATION Benchmarks

We have performed tests on several publicly available benchmarks that use POSIX threads.

- 1. ROSACE (Research Open-Source Avionics and Control Engineering)

- 2. TACLeBench (Timing Analysis on Code-Level ) powerwindow

Two self-developed Benchmarks

- 1. Threadep

- 2. SimulationofAutomotive

https://github.com/mahsa-poorjafari/SA SimulationofAutomotive

# EVALUATION Assessment Criteria

### Qualitative Measure:

Adequacy of the abstraction level

### Quantitative Measure:

· Percentage of the reduction in elements and relations achieved with ArchViMP

$$Element(El)/Relation(Re)\ Reduction\ Percentage = \\ (1 - \frac{number\ of\ El/Re\ in\ an\ abstract\ view}{number\ of\ El/Re\ in\ the\ raw\ representation})*100$$

## Results

### Evaluation of benchmarks in architectural views

- Element Reduction Percentage (ERP)

- Relation Reduction Percentage (RRP)

- o ROSACE (R)

- Threadep (TE)

- TACLeBench powerwindow (TB)

- SimulationOfAutomotive (SA)

- No view (-)

- Logical Context (LC)

- Functional Flow Sub-view (FFSV)

- Execution Control Flow Sub-view (ECFSV)

| <b>Evaluation Parameter</b> | R     | TE    | ТВ    | SA  |

|-----------------------------|-------|-------|-------|-----|

| ERP - LC at level 3         | _     | _     | 45%   | -   |

| RRP - LC at level 3         | -     | -     | 60%   | _   |

| ERP - FFSV at level 2       | 50%   | 51.7% | 63.6% | 25% |

| RRP - FFSV at level 2       | 83.3% | 88%   | -     | 71% |

| ERP - ECFSV at level 2      | 60%   | 58.6% | -     | 79% |

| RRP - ECFSV at level 2      | 92%   | 92%   | -     | 92% |

## Conclusion and Future work

- automatic visualization of the concurrency related behavior within multiple concurrent architectural views and

- reduction of the number of elements shown on a single screen, by using different viewpoints and abstraction levels.

- Further refinement and combination of logical rules to:

- Cover more corner cases

- Cover more dependencies

# Thank you

Monireh Pourjafarian

Jasmin Jahić

mpourjaf@rhrk.uni-kl.de

jj542@cam.ac.uk

Technical University of Kaiserslautern

University of Cambridge

Kaiserslautern, Germany | Cambridge, UK