# THE UNIVERSITY OF TOKYO

# Contact

[name] Eishi Arima [organization] The University of Tokyo [email] <u>arima@cc.u-tokyo.ac.jp</u> [web] http://www.cspp.cc.u-tokyo.ac.jp/arima/index-e.html

# **Toward Footprint-Aware Power Shifting for Hybrid Memory Based Systems**

Eishi Arima The University of Tokyo

Toshihiro Hanawa The University of Tokyo

# Concept

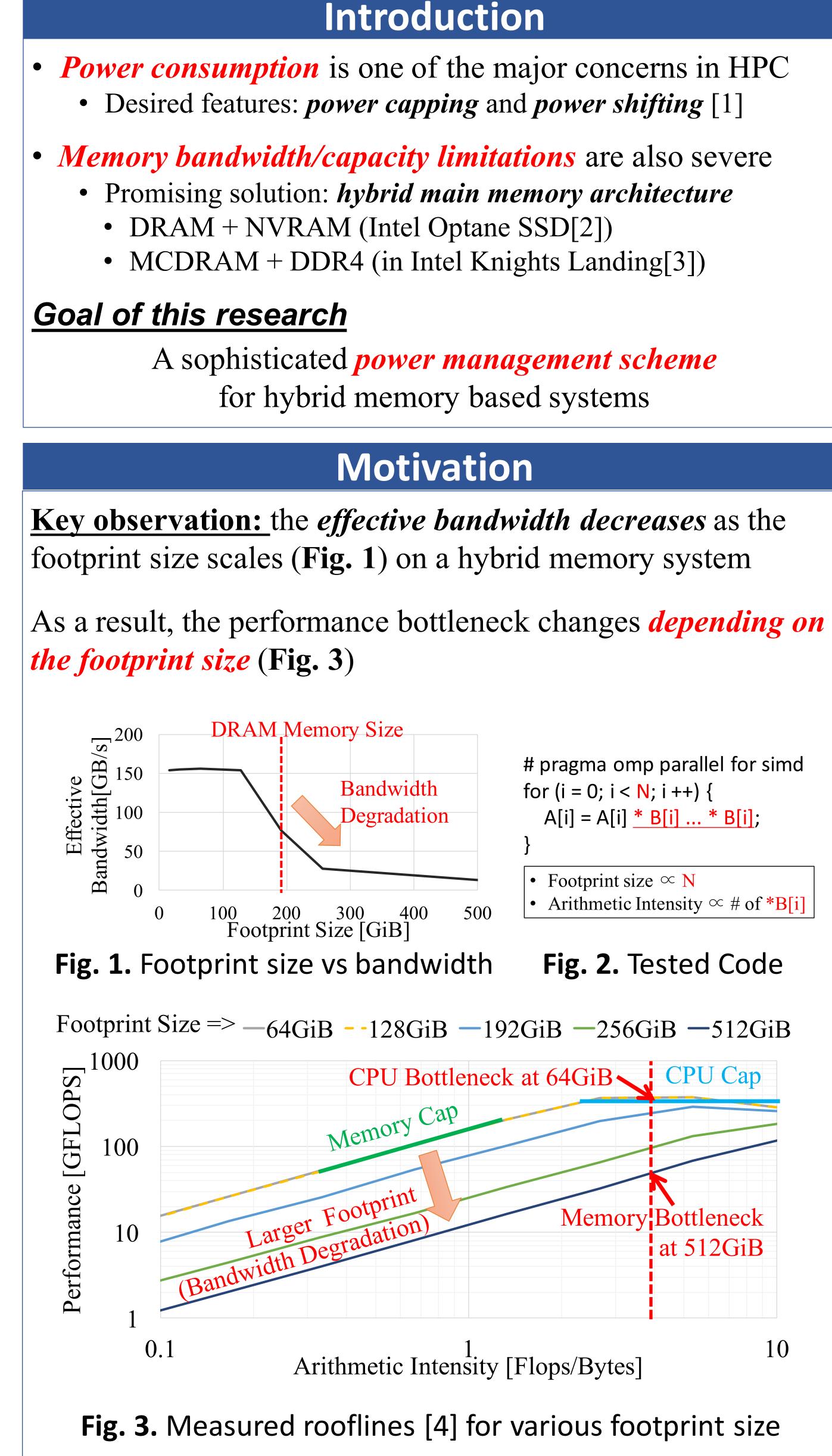

**Objective:** Maximizing performance (*Perf*) under a total power constraint (*P<sub>total</sub>*) by controlling *CPU/memory power*  $(P_{cpu}/P_{mem})$  for a given *footprint (or problem) size* (S)

### Formulation:

max **Perf(P<sub>cpu</sub>, P<sub>mem</sub>, S)** s.t.  $P_{cpu} + P_{mem} \leq P_{total}$

CPU

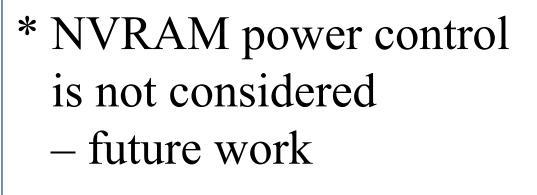

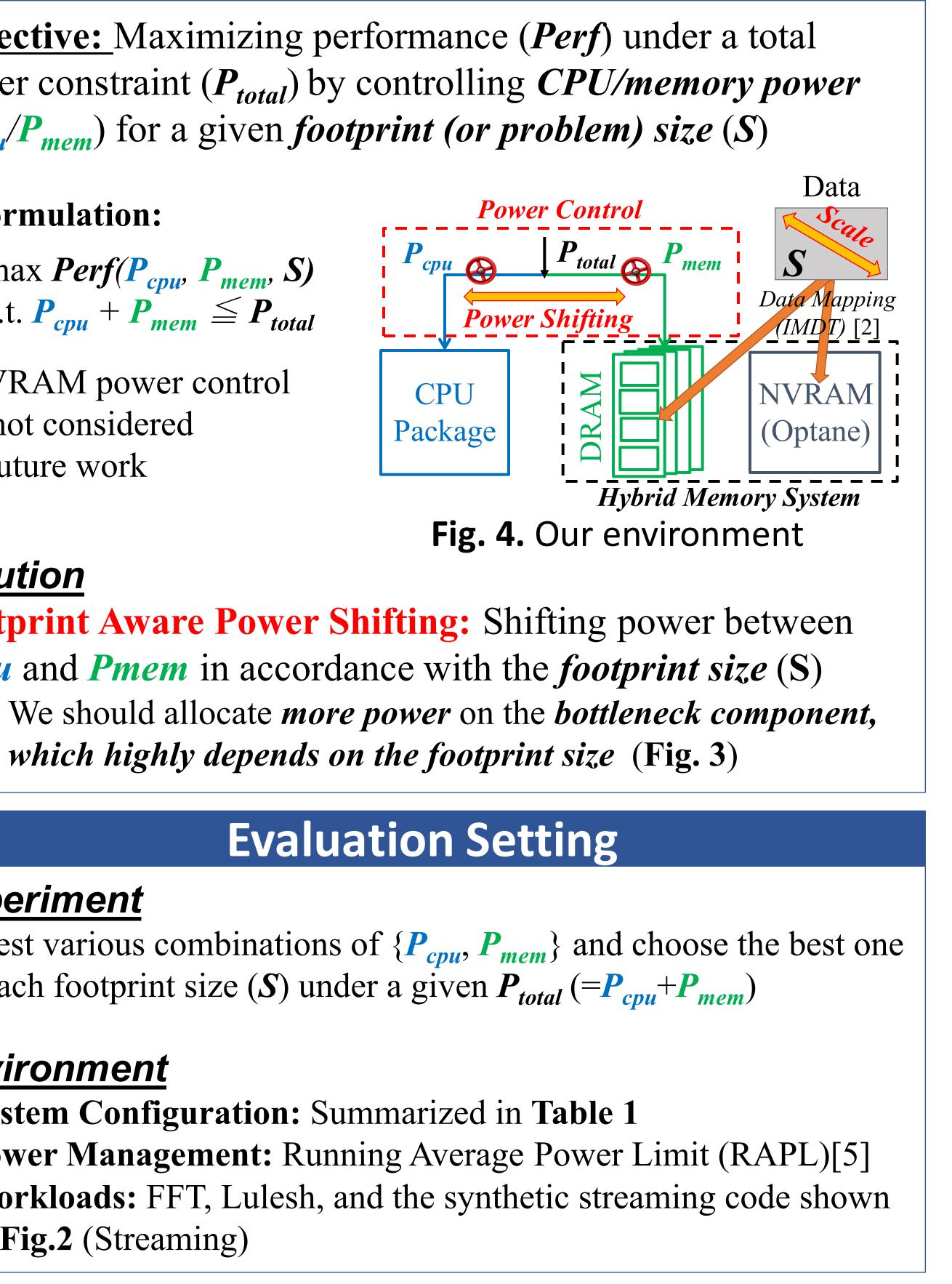

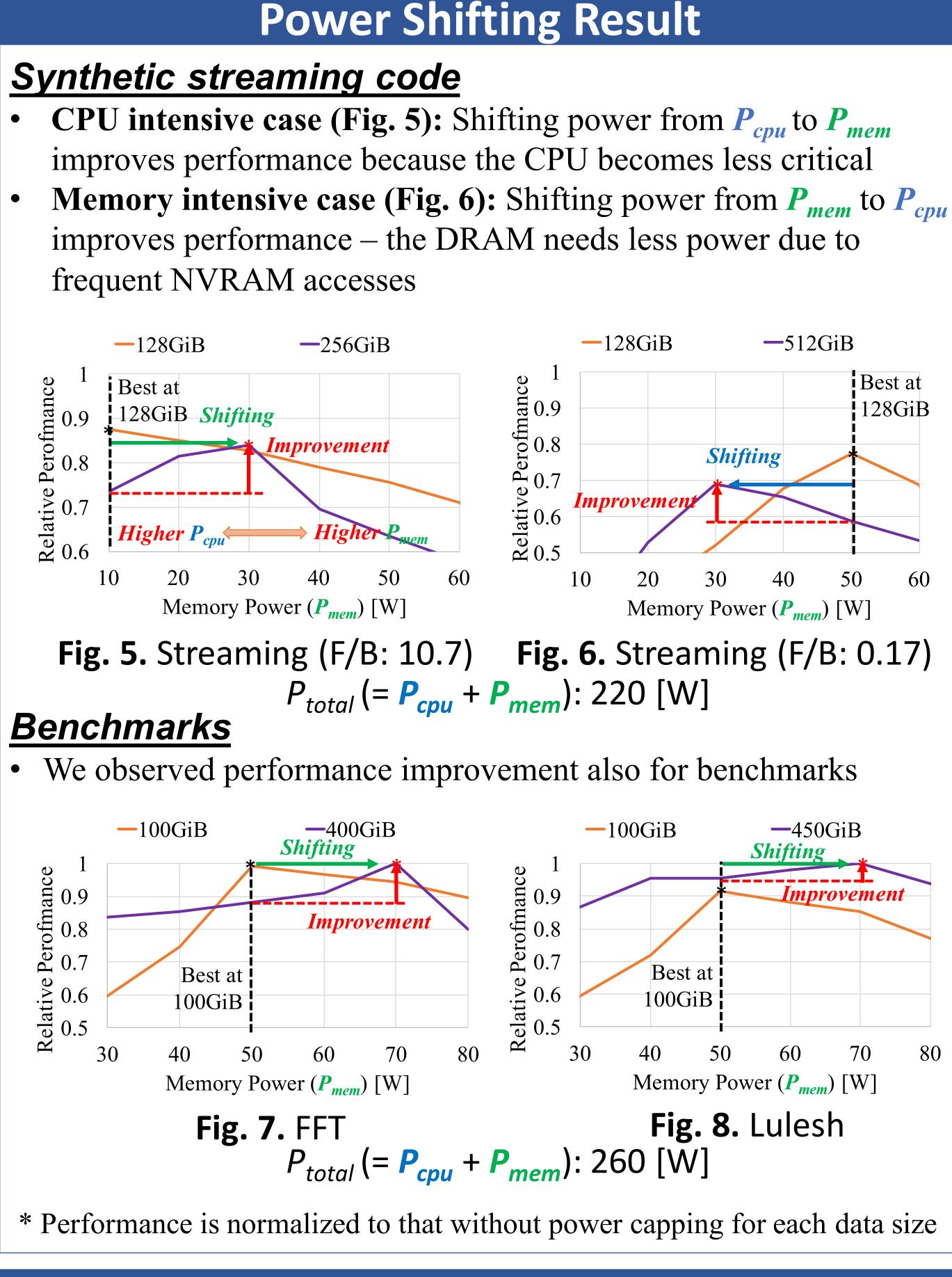

## Solution

Footprint Aware Power Shifting: Shifting power between *Pcpu* and *Pmem* in accordance with the **footprint size** (S) We should allocate *more power* on the *bottleneck component*,

**Evaluation Setting**

### Experiment

We test various combinations of  $\{P_{cpu}, P_{mem}\}$  and choose the best one for each footprint size (S) under a given  $P_{total} (= P_{cpu} + P_{mem})$

### Environment

- **System Configuration:** Summarized in **Table 1**

- **Power Management:** Running Average Power Limit (RAPL)[5]

- Workloads: FFT, Lulesh, and the synthetic streaming code shown in **Fig.2** (Streaming)

### Table 1. System Configuration

|                  | •                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------|

| CPU<br>Package   | Xeon Gold 6154 Processo<br>TDP 200W x2 sockets                                                   |

| Memory<br>System | DRAM: DDR4-2666 x12<br>NVRAM: Intel Optane S<br>2.4GB/s(read), 2.0GB/s(v<br>Data management: IMD |

| OS               | Cent OS 7.4                                                                                      |

| Compiler         | Intel C++/Fortran Compil<br><b>Options:</b> -O3, -qopenmp                                        |

# Acknowledgement

This work is partly supported by JSPS Grant-in-Aid for Research Activity Start-up (JP16H06677), JSPS Grant-in-Aid for Early-Career Scientists (JP18K18021), and Research on Processor Architecture, Power Management, System Software and Numerical Libraries for the Post K Computer System of RIKEN.

Martin Schulz Technical University of Munich

sor (Skylake), 18 cores, 3.0GHz,

2 modules, 12ch, 192GiB SSD P4800X, 375GB, write) x2 cards DT [2]

iler 17.0.4

### Conclusions

Future Work

- Including NVRAM power management

- Knights Landing

# References

[1] Lefurgy, C., et al. "Power Capping: A Prelude to Power Shifting". Cluster Computing 11, 2 (2008), 183–195. [2] Intel. "Intel® Memory Drive Technology, Set Up and Configuration Guide", 2017. [3] Jeffers, J., et al. "Intel Xeon Phi Processor High Performance Programming: Knights Landing Edition". Morgan Kaufmann Publishers Inc., San Francisco, CA, USA, 2016.

[4] Williams, S., et al. "Roofline: An Insightful Visual Performance Model for Multicore Architectures". Communications of the ACM 52, 4 (2009), 65–76. [5] Intel. "Intel® 64 and ia-32 Architectures Software Developer's Manual", System Programming Guide, 2017.

Technical University of Munich

# **Conclusions and Future Work**

### *Footprint-aware power shifting is promising* to improve the performance of power constrained hybrid memory based systems

• Developing a software framework, a performance model, and a power allocation algorithm to realize our proposal • Evaluating with other hybrid memory based systems such as Intel